O subsistema de DMA no PC

é baseado no controlador Intel 8237.

O 8237 é um controlador

de DMA que permite transferir informação entre a memória

e uma porta de entrada/saída com velocidades da ordem de 1,6 MB/s.

Nem todas as aplicações de

DMA envolvem periféricos de alta velocidade.

Também se pode usar impressoras com buffer com interface de DMA. Sempre

que a flag BUSY/READY da impressora indicar READY, o buffer da impressora

pode ser preenchido usando DMA a alta velocidade, a transferência por

DMA fica completa e o microprocessador retorna o processamento normal quando

a impressora esvaziar o buffer.

A vantagem em usar um controlador de DMA

(um DMAC) para esta aplicação é que o controlador pode

ser programado para manter o registo de endereço inicial e o número

de palavras sem intervenção do CPU. Se forem usadas interrupções,

seria necessária uma rotina de serviço da interrupção

e seria gasto tempo considerável de processamento no armazenamento

e na recuperação de variáveis.

A desvantagem do DMA é que o processador

tem que parar enquanto ocorre uma transferência por DMA. Isto não

é uma verdadeira desvantagem quando a transferência ocorre em

explosões (bursts) tal como no exemplo da impressora. Por outro lado,

é oferecida uma melhor solução por parte das interrupções

se a impressora não tiver um buffer e o DMA tiver de inserir estados

de espera (WAIT) para se sincronizar com taxa de informação

da impressora.

Outra desvantagem do DMA é que não é possível

fazer processamento a priori nem a posteriori pelo DMAC. Se tal for necessário,

terá de ser feito antes ou após a informação ser

transferida.

No passado a maior limitação

no uso de DMA foi a grande complexidade de concepção do DMAC.

É aqui que entra o 8237. O 8237 fornece todas as características

requeridas para transferências por DMA num só chip de 40 pinos

e incorpora-se directamente na arquitectura de sistema de três estados.

Entre as características do 8237 encontram-se as seguintes:

- Existem quatro canais de DMA

- Cada canal é capaz de transferir

até 64K bytes

- Pode se escolher entre prioridades

fixas ou rotativas

- O hardware ou o software podem requerer

transferência por DMA

- Podem ser especificadas transferências

de blocos de bytes ou de bytes individuais

- São possíveis transferências

de informação entre I/O e a memória e de memória

para memória.

Interface do 8237

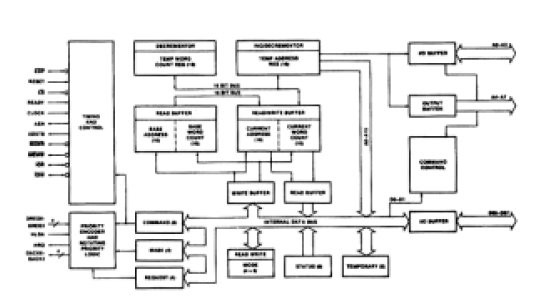

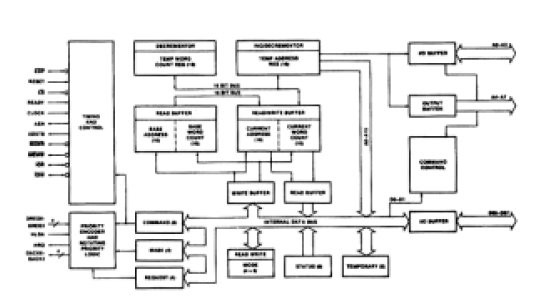

A figura a seguir representa o diagrama de blocos

do 8237.

Existe um problema em grandes sistemas onde todas as linhas de dados no módulo

do CPU têm buffer. É que apesar de os buffers “verem”

altas impedâncias nas suas entradas (do microprocessador de três

estados), normalmente eles irão converter isto em níveis de

1 lógico nas suas saídas, originando problemas de contenda do

barramento com o DMAC. Por esta razão os módulos de CPU devem

incluir um sinal que permita aos buffers de barramento ter três estados.

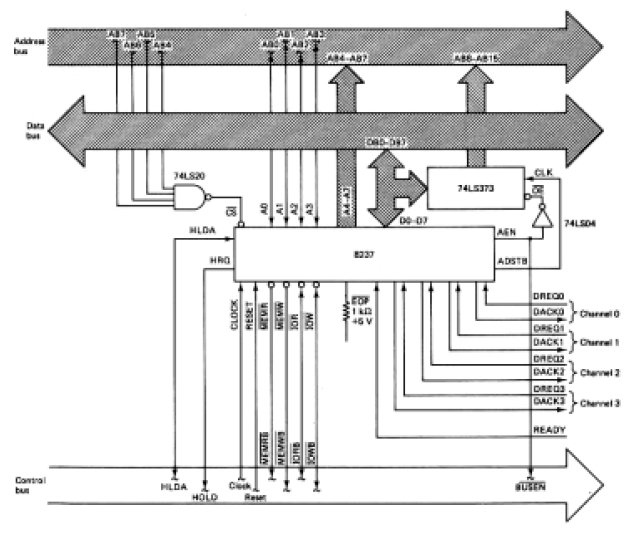

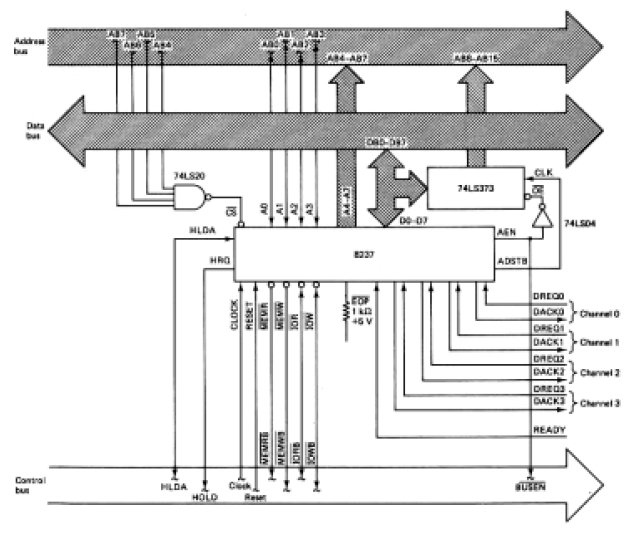

Na seguinte figura é

mostrado como é que se pode fazer a interface do 8237 com um módulo

de CPU.

É de reparar que

é necessário fixar um endereço de alta ordem. Durante

o tempo em que o ADSTB está a 1 e quando estiver a ocorrer uma transferência

por DMA, D0-D7 vão manter os bits de ordem mais alta do endereço.

O flanco descendente de ADSTB fixa este byte no latch 74LS373. Para o resto

de transferência por DMA, D0-D7 funcionam como barramento bidireccional

de dados.

De seguida vão ser

enunciados os passos requeridos para efectuar uma transferência de informação

com um periférico.

-

Antes da transferência

ocorrer, deve se programar o DMAC com o endereço de memória,

o número de bytes e o tipo de transferência. No caso do 8237,

o DMAC aparenta ser 16 portas de entrada/saída consecutivas seleccionadas

com A3-A0 e IOR e IOW. É de notar que o dispositivo não pode

mapeado por memória; MEMR e MEMW são somente pinos de saída.

-

Agora pode ser pedida

uma transferência por DMA num dos quatro canais por um periférico

activando DREQ.

-

Se o 8237 estiver activado

e o canal activado não estiver mascarado, o DMAC activa HRQ, pedindo

um estado de espera (HOLD) do CPU.

-

O CPU responde completando

o ciclo de instrução actual, colocando os seus barramentos

em alta impedância e enviando HLDA.

-

O DMAC avisa o periférico

deste reconhecimento enviando DACK para o periférico. Este sinal

é normalmente usado para o chip select (CS) das portas de dados dos

periféricos.

-

Agora o 8237 envia

o endereço em D7-D0 e coloca AEN e ADSTB a 1. Este endereço

representa a origem ou o destino da transferência de informação.

O AEN activa as saídas de alta impedância do latch e também

é usado para desactivar os barramentos do sistema através

de BUSEN.

-

O ADSTB vai a 0, fazendo

com que endereço de alta ordem seja fixado. D0-D7 mudam para se tornarem

o barramento de informação e A0-A7 o barramento de endereço

de baixa ordem.

-

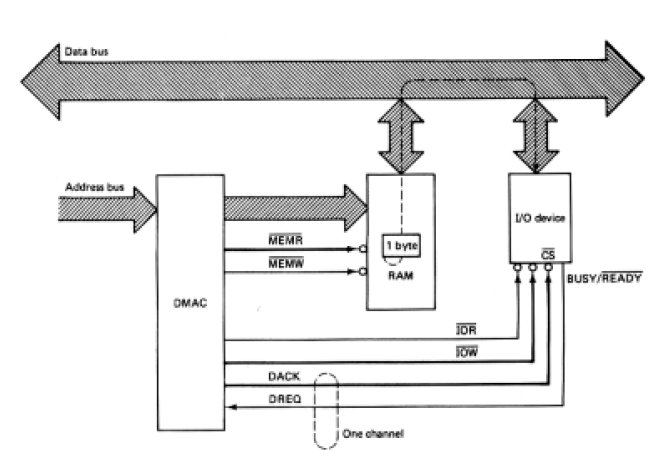

Agora o DMAC controla

os barramentos e são permitidos os três tipos de transferência

de informação, tal como demonstrado na figura abaixo. Nesta

figura, a carregado, está a transferência de um byte de informação

da memória para um dispositivo de entrada/saída. Repare-se

na condição não usual do controlo de barramento –

estão activos dois sinais em simultâneo: MEMR e IOW. Apesar

de isto nunca poder acontecer quando o CPU tem o controlo, é normal

quando quem tem o controlo é o DMAC. A informação lida

da RAM é directamente enviada para o dispositivo de entrada/saída;

ela não vai pelo DMAC.

-

Só é

necessário um canal do 8237 para a transferência. No caso especial

de uma transferência de memória para memória, são

necessários dois canais: um é programado com o endereço

origem (o 8237 requer o canal 0) e o outro com o endereço de destino

(o 8237 requer o canal 1). Neste caso não são

necessários DREQ nem DACK.

-

A informação

é transferida entre a RAM e o dispositivo de entrada/saída

até que o contador de bytes seja zero (chamada contagem terminal).

Também é possível parar a transferência com uma

entrada externa EOP (End Of Process) no DMAC. Em qualquer caso, HRQ e AEN

são removidos, desistindo do controlo do barramento para o processador.

Tempo de resposta e taxa de transferência

Tal como mencionado anteriormente o CPU responde

dentro de um ciclo de máquina dum pedido de HOLD. Isto significa que

podem decorrer um máximo de seis T estados entre o pedido de DMA e

o começo da transferência por DMA. Como termo de comparação

temos que para responder a um pedido de interrupção são

necessários 12 a 31 T estados.

Quando estiver para ocorrer uma transferência por DMA, normalmente o

tempo de resposta não é o problema principal. Isto porque o

processador de DMA está feito para transferir grandes blocos de informação,

ao contrário das interrupções ou do polling em que o

processador tem que monitorar uma flag de BUSY/READY e depois responder rapidamente

com um byte de informação antes de ocorrer a próxima

transacção.

O 8237 tem dois modos básicos de operação: em repouso

(idle) ou activo

(active). No estado de repouso pode ser programado pelo processador para um

próximo

estado activo durante o qual irá ocorrer a transferência por

DMA.

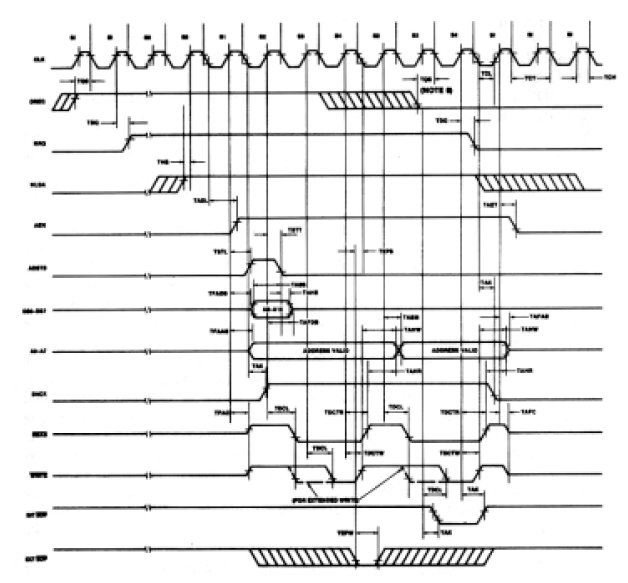

Na figura em baixo pode-se

ver as actividades que ocorrem durante cada um dos seis estados de relógio

possíveis.

Após ocorrer um DREQ, o

DMAC passa do estado S1 para o estado S0, esperando HLDA do processador. No

estado S1 é enviado o endereço de alta ordem. Note-se que este

endereço só muda uma vez em cada 256 transferências de

informação. Por esta razão, o 8237 apaga automaticamente

o estado S1 excepto quando tem de mudar o endereço de alta ordem.

Durante S2 é enviado o endereço de baixa ordem e durante S3

aparecem os sinais de controlo. A transferência de informação

propriamente dita ocorre durante o estado S4. Assumindo que o endereço

de alta ordem não muda, serão necessários três

estados de relógio (S2, S3 e S4) para uma transferência de informação.

A taxa de transferência para o 8237A é de 1,6 MB/s. Claro que

quer o dispositivo de I/O quer a memória devem ser capazes de manter

esta alta taxa de transferência. Para memórias de semicondutores

isto não constitui um problema.

Contudo, o dispositivo de I/O pode ser outro assunto. Uma das aplicações

mais comuns do DMA é fazer de interface com um drive de disco em série

– um disco duro ou um floppy disk.

Considere-se uma floppy disk de

dupla densidade de 5 ¼ polegadas que requer um novo byte de informação

cada 32 µs. Para fazer interface com este tipo de periféricos

deve ser usada a entrada READY do 8237. Esta linha é posta a 0 pelo

controlador do periférico enquanto ele recebe (ou escreve) um novo

byte de informação.

A entrada READY do DMAC é semelhante à entrada READY do microprocessador

e é amostrada durante S3. Se esta entrada for 0, os três barramentos

“marcam tempo”, segurando informação válida

até READY ser novamente 1.

Apesar de a interface de floppy disk não o requerer, o 8237 é

capaz de uma taxa de informação ainda maior se for usado tempo

comprimido. Neste modo é suprimido o estado S3; só é

usado para expandir o comprimento do pulso dos sinais de controlo IOR e IOW,

permitindo transferências de informação só com

os estados S2 e S4. Isto iria requerer dispositivos de memória com

tempos de acesso inferiores a 400 ns para o 8237A - 5.

As transferências de memória

para memória requerem o dobro do tempo das transferências entre

memória e um dispositivo entrada/saída. Isto porque é

necessário um conjunto de S estados para ler um byte de informação

e outro para escrevê-lo, pois MEMR e MEMW não podem ser permitidas

ser 0 simultaneamente como acontece com os sinais de controlo de memória

e de entrada/saída. Além disso é necessário um

registo temporário dentro do 8237 para guardar a informação

antes de ocorrer o ciclo de escrita. As transferências entre memórias

são úteis quando se pretende transferir um bloco de informação

grande ou quando um bloco de memória é para ser preenchido com

um determinado caracter.

Programação do 8237

Cada canal do 8237 tem um registo

de 16 bits do endereço actual e um registo de 16 bits da palavra actual.

O registo do endereço actual guarda o endereço de memória

para a próxima transferência por DMA. O registo da palavra actual

age como um contador em modo decrescente de 16 bits e é programado

com o número total de bytes a ser transferido menos um. A contagem

terminal ocorre quando este registo passa de 0000H para FFFFH.

Cada um destes registos é suportado por registo de endereço

base e por um registo de palavra base que contêm os valores iniciais

quando programados. Isto permite que ocorra uma inicialização

automática de uma sequência (se programada) quando ocorrer a

contagem terminal (ou EOP).

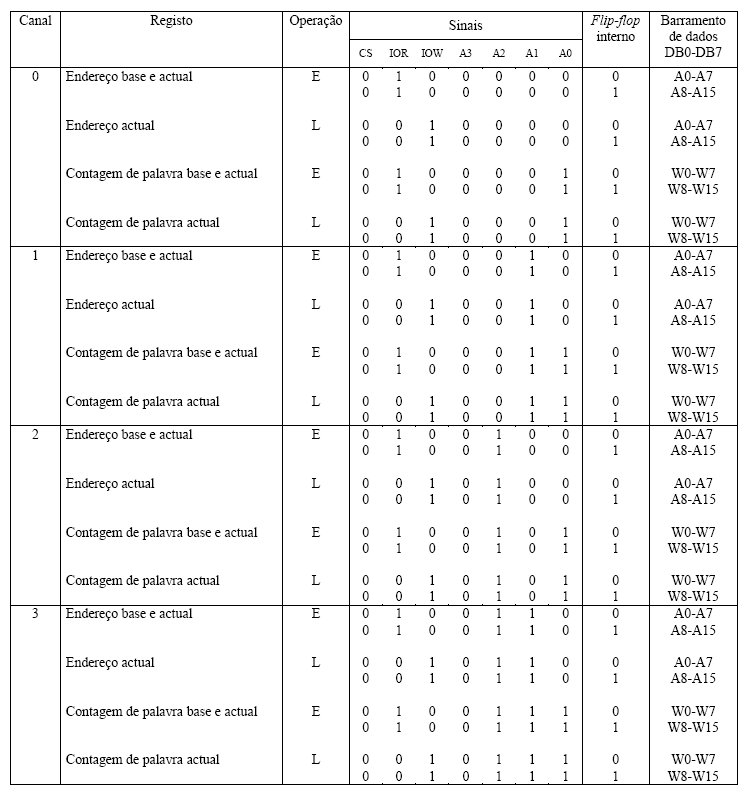

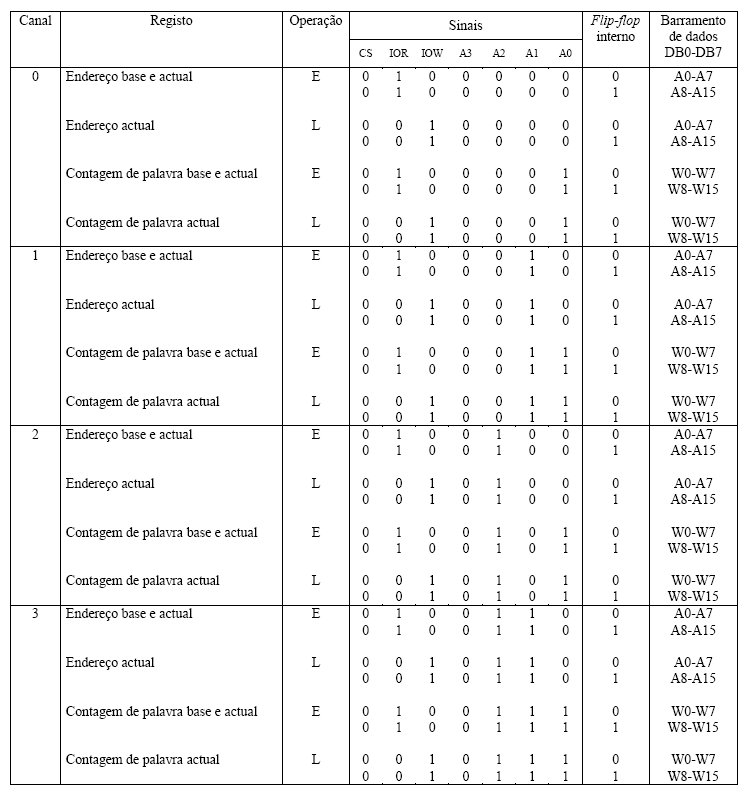

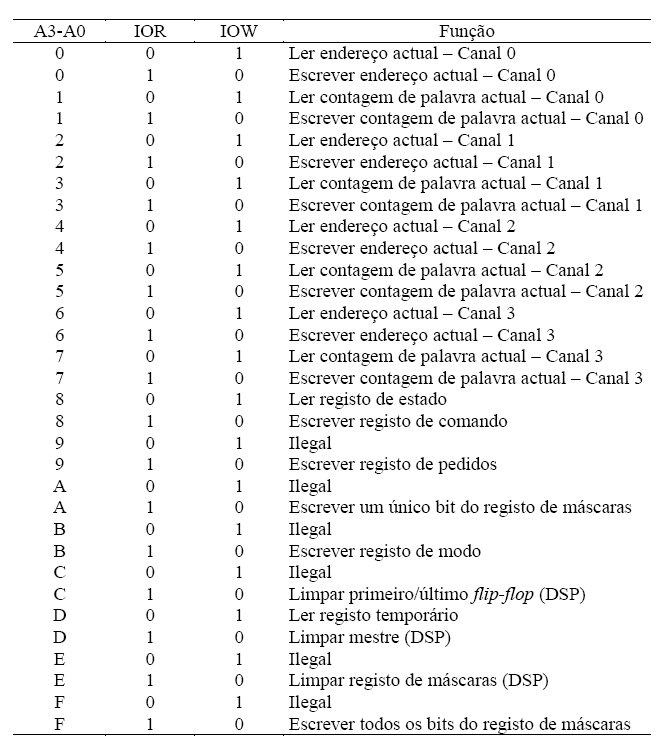

A Tabela abaixo indica os códigos

dos sinais de controlo necessários para aceder aos registos de cada

canal. Repare-se que os registos do endereço actual e da contagem de

palavra só podem ser lidos, não podem ser escritos. Como o endereço

base e a contagem de palavras provavelmente requerem 16 bits, é usado

um flip-flop interno para encaminhar estes dois bytes para o DMAC. Deste modo

a primeira escrita para os registos dos endereços base e actual é

interpretada como o endereço de baixa ordem e a segunda escrita como

o endereço de alta ordem. É usado um esquema semelhante com

o registo de contagem de palavra.

No 8237 também deve ser

programado o modo de transferência por DMA.

Existem quatro escolhas:

1. Transferência simples:

É transferido um único

byte, a contagem de palavras é decrementada e o registo de endereço

actual é incrementado ou decrementado conforme programado. DREQ deve

ser mantido activo até se receber DACK. Se DREQ estiver activo durante

a transferência, o controlo será devolvido ao microprocessador

por um ciclo de máquina antes de iniciar a próxima transferência.

2. Transferência

de bloco:

A informação é

transferida até que ocorra TC (contagem terminal) ou EOP. DREQ deve

ser mantido activo até que ocorra DACK.

3. Transferência

por pedido:

A informação é

transferida enquanto DRQE estiver activo. Quando DREQ ficar inactivo, o

endereço actual e a contagem de palavra não mudam, permitindo

ao dispositivo de I/O retomar a transferência onde a deixou. TC ou

EOP terminarão o processo.

4. Modo em cascata:

Neste modo um 8237 age

como Mestre e outro como Escravo. Cada um dos escravos é programado

para um dos três modos de transferência descritos acima. Cada

escravo fornece o endereço de memória para a transferência,

mas o mestre dá prioridade aos pedidos de HOLD dos

escravos.

Adicionalmente aos quatro modos

listados, pode ser especificada uma transferência de memória

para memória. Este modo é limitado a transferências de

blocos e o canal 0 deve ser usado para a origem e o canal 1 para o destino.

São usados quatro registos para programar o modo de transferência

e para seleccionar várias características de operação

do 8237. Cada um destes registos só permite ser escrito.

1. Registo de comando:

Este registo controla a operação

do 8237. Repare-se que o chip pode ser desactivado fazendo com que o bit

D2 seja 1. Se for seleccionada a rotação de prioridades, o

último DREQ atendido irá ter a prioridade mais baixa.

2. Registo de modo:

A porção de acesso

à memória da transferência por DMA pode ser programado

para uma operação de leitura, escrita ou verificação.

Quando programação para verificar transferências, o

8237 envia endereços mas não os sinais de controlo.

3. Registo de pedidos:

Este registo permite ao software

iniciar a transferência por DMA em vez do DREQ. Quando programado

para transferências de memória para memória, activa

o bit de pedido para o canal 0 começa a transferência. Os pedidos

de software não são mascaráveis.

4. Registo de máscaras:

Este registo é usado

para mascarar o DREQ para cada canal. Limpar o bit de máscara activa

aquele canal para pedidos de DMA. Os bits de máscara podem ser limpos

individualmente ou colectivamente.

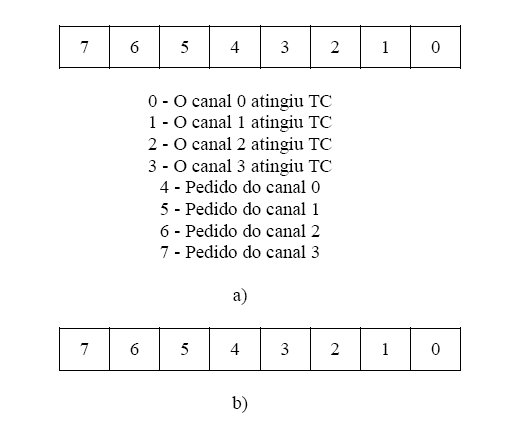

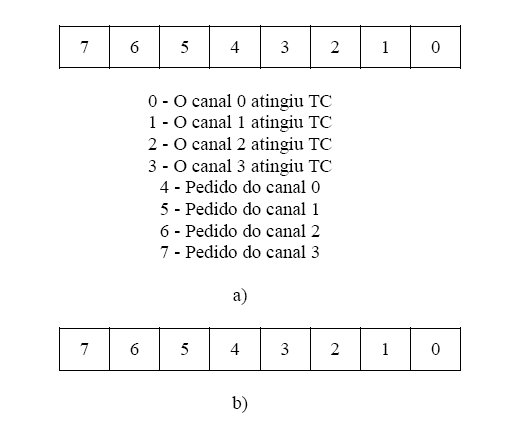

Há dois registos que só podem ser lidos: são o registo

de estados e o registo temporário, mostrados na figura em anexo (a)

e b), respectivamente.

Três portas do 8237 não

são realmente portas mas usam o pulso de escolha de dispositivo criado

por uma instrução de saída (OUT).

1. Limpar primeiro/último

flip-flop:

Isto faz o reset do flip-flop interno

para as portas 0-7 (ver Tabela 5.2). O próximo endereço de

memória irá deste modo ser o byte de baixa ordem para o endereço

de memória ou para a contagem de palavra.

2. Limpar mestre:

O 8237 entra no estado de repouso

com os registos de comando, estado, pedidos e temporários e o flip-flop

interno todos em reset e com todos os bits do registo de máscaras

em set.

3. Limpar registo de máscaras:

Este comando activa todos os quatro

canais a aceitar pedidos de DMA nas suas entradas DREQ limpando todos os

bits no registo de máscaras.

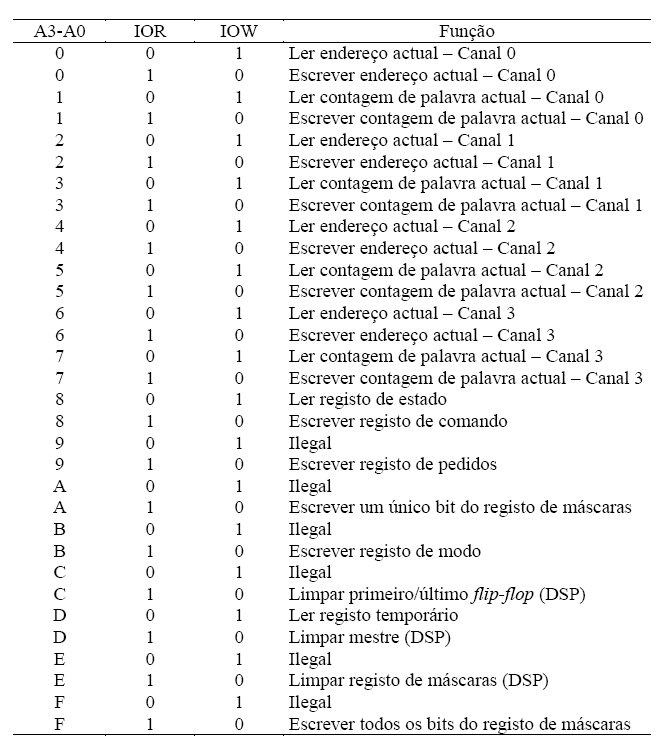

A Tabela em baixo lista a funções

de leitura e escrita associadas com cada um dos 16 endereços (base)

de porta do DMAC. Utilizando o descodificador, o 8237 requer as portas entre

F0H e FFH (as portas FC, FD e FE são controladas pelos pulsos de selecção

de dispositivo e não transferem informação).

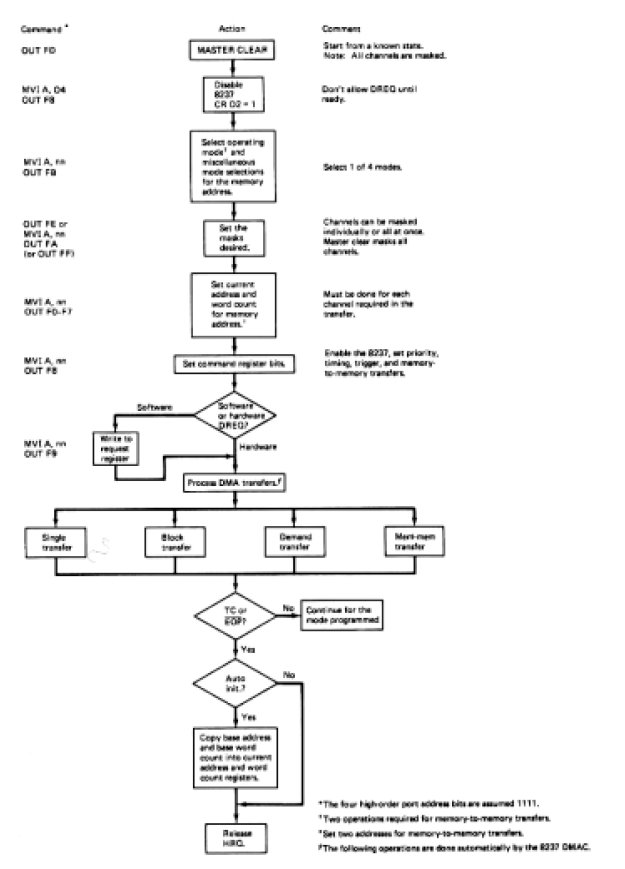

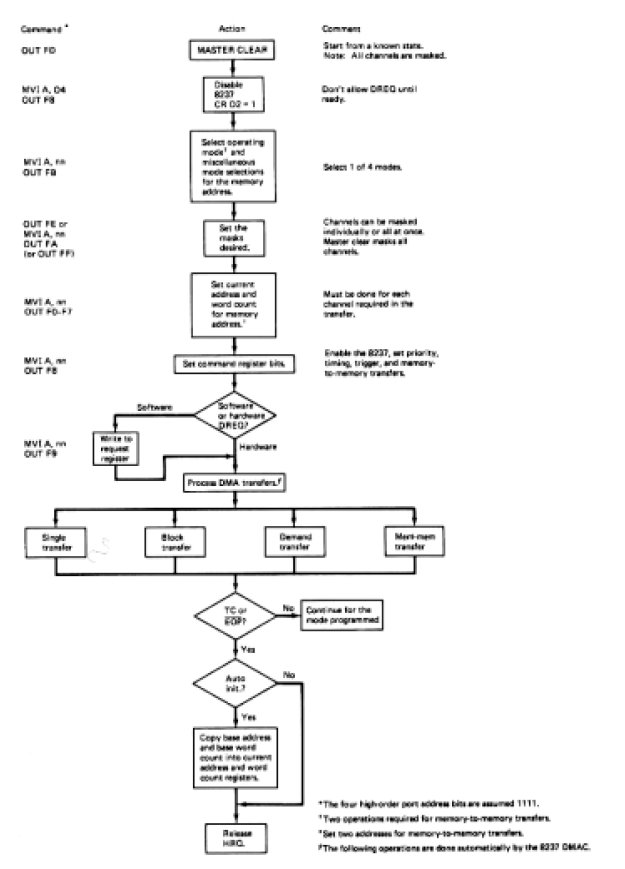

A figura a seguir mostra um fluxograma

dos passos necessários para inicializar o 8237 e mostra as acções

tomadas pelo DMAC uma vez programado. Repare-se que é aconselhável

desactivar o DMAC até se completar a inicialização se

um DREQ for recebido durante este tempo.

<<anterior

seguinte>>