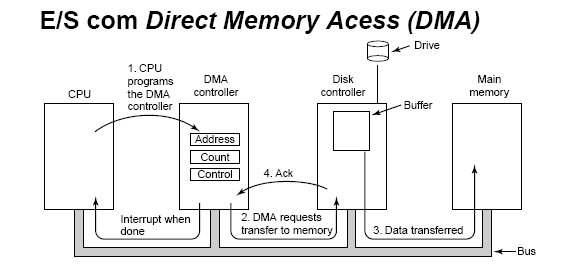

Exemplo de uma Tranferência de dados através de DMA

Aqui está um exemplo dos passos que ocorrem para provocar uma transferência por DMA. Para demonstrar vamo-nos basear que o controlador de disquetes acabou de ler um Byte de uma disquete e quer que o DMA o coloque na memória no endereço 0x00123456.

O processo começa

com o controlador de disquetes a pedir ao canal DRQ2 para alertar o controlador

de DMA.

O controlador de DMA irá receber o alerta do DRQ2. O controlador de

DMA irá então verificar se o canal 2 foi programado e está

activo. O controlador de DMA também irá verificar se os outros

canais de DMA estão todos inactivos ou se não têm uma

prioridade maior.

Uma vez concluídas esta verificações, o DMA pede ao CPU para libertar o BUS para que o DMA o possa utilizar. O DMA pede o BUS utilizando o sinal HRQ que vai para o CPU. O CPU detecta o sinal HRQ, e irá terminar de executar a instrução actual. Quando o processador chegar a um estado em que possa libertar o Bus assim o fará. Todos os sinais que são gerados normalmente pelo CPU (-MEMR, -MEMW, -IOR, -IOW e mais alguns), serão colocados na condição de três estados (neither high or low), depois o CPU comunica ao sinal HLDA, que por sua vez comunica ao controlador de DMA que este se encontra em posse do BUS.

Dependendo do processador, o CPU poderá executar algumas instruções adicionais, visto que agora não controla o BUS. O CPU pode eventualmente ter que esperar quando chega uma instrução que necessita de ler alguma coisa da memória que não está na cache interna do processador ou na pipeline. Agora que o DMA está a comandar, este activa os seus sinais de output (-MEMR, -MEMW, -IOR, -IOW), e o endereço de Output do DMA é colocado a 0x3456, que irá ser usado para direccionar o Byte que está prestes a ser transferido para um local de memória especifico.

O DMA irá então

permitir que o dispositivo que requereu a transferência por DMA saiba

que a transferência irá começar. Isto é feito usando

o sinal DACK, ou no caso do controlador de disquetes, DACK2. O controlador

de disquetes está agora responsável em colocar o Byte que irá

ser transmitido no Bus. A não ser que o controlador de disquetes precise

de mais tempo para colocar o Byte no Bus ( se o periférico necessitar

de mais tempo, este irá avisar o DMA através do sinal READY),

o DMA irá esperar um DMA clock, então desligará o sinal

MEMW e IOR para que a memória guarde o Byte que se encontrava no Bus.

Ao desligar estes sinais o controlador de disquetes também saberá

que o Byte foi transferido.