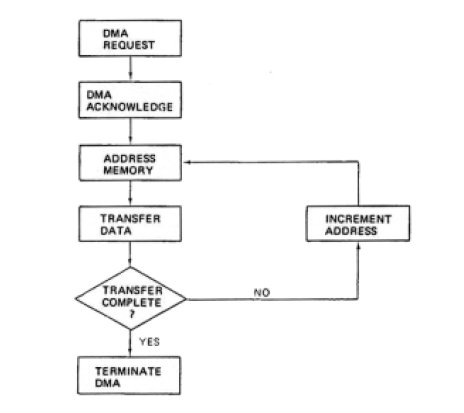

No passo 1 o periférico requisita uma transferência por DMA activando a entrada correspondente do processador. Este avisa a sua recepção depois de acabar o ciclo de instrução que estava a executar, desactivando de seguida os barramentos de endereço e informação. A maior parte dos processadores com facilidade de DMA usam buffers de saída com três estados para facilitar a sua desactivação. Durante este estado o processador permanece numa situação em que não realiza qualquer operação.

Lógica exterior (controlador de DMA) toma conta dos barramentos de endereço e informação e fornece um endereço para o sistema de memória (passo 3). Dá-se, então, a transferência de informação entre a memória e o periférico seleccionado. No caso da transferência envolver um bloco de informação, o controlador deve fornecer o endereço inicial, incrementar os endereços de memória após cada transferência e manter um contador que conte o número de palavras transferidas. Após a transferência, o controlador termina o DMA desactivando o sinal aplicado ao microprocessador (HOLD, etc.) o que completa o passo 5.

A figura em anexo contém

um fluxograma de uma transferência de DMA típica.

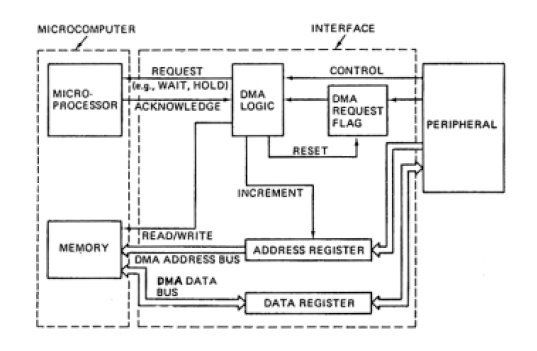

A seguir encontra-se um diagrama

de blocos de um sistema de DMA.

É fornecido à lógica de DMA a informação

necessária para especificar se se trata de uma operação

de leitura ou escrita na memória. O registo de endereço é

carregado com o endereço inicial, dando-se de seguida uma transferência

entre o periférico e a memória. Após cada transferência

o registo de endereço é incrementado para seleccionar o endereço

seguinte. Quando a transferência tiver terminado é feito o

reset do pedido de DMA, o que autoriza o processador a retornar as suas

funções normais.

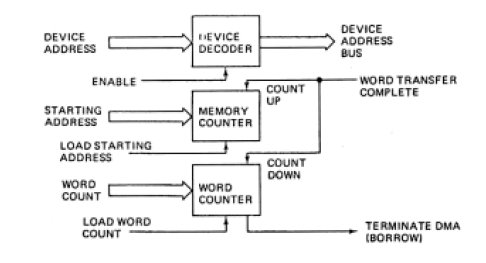

Lógica de DMA necessária para efectuar as operações descritas.

O DEVICE ADDRESS activa o periférico

apropriado através do descodificador a que liga. O endereço

inicial (starting address) e o número de palavras a transferir (word

count) são carregados nos contadores de memória e de palavra.

A primeira palavra do bloco é então transferida, sendo o contador

de memória incrementado pelo sinal COUNT UP e o contador de palavra

decrementado pela entrada de COUNT DOWN. A transferência prossegue decrementando-se

o contador de palavras até atingir zero, altura em que é gerado

um sinal para terminar a operação de DMA. Nas transferências

que envolvem mais que um bloco deve acrescentar-se a esta lógica um

contador de bloco.

Existem duas classes de DMA:

No DMA sequencial o controlador de DMA (DMAC) efectua uma operação de leitura mandando vir o byte de informação do DMAC. De seguida é efectuada uma operação de escrita transferindo o byte de informação para a porta de entrada/saída. Também é possível a sequência oposta – ler um byte da porta I/O, escrever um byte na memória. Normalmente são necessários dois a quatro períodos de relógio para cada operação de leitura ou escrita. O DMA simultâneo fornece as transferências mais rápidas. Com esta técnica as operações de leitura e de escrita são feitas ao mesmo tempo. Isto requer que MEMR e IOW (ou IOR e MEMW) estejam activas simultaneamente. Deste modo a informação não passa pelo DMAC mas vai directamente da memória para a porta I/O ou vice-versa. Como resultado temos uma melhoria de duas vezes na velocidade comparado com o DMA sequencial.

Em qualquer dos casos a

transferência de informação é feita completamente

em hardware envolvendo só o DMAC, o periférico e a memória

principal. Como o CPU não está envolvido não há

overhead de software. Os pedidos de DMA tomam precedência sobre todas

as outras actividades do barramento incluindo interrupções.

De facto, não será reconhecida qualquer interrupção

– mascarável ou não-mascarável – durante

um pedido de DMA.

Existem quatro tipos de transferência

por DMA:

1. Memória para periférico

2. Periférico para memória

3. Memória para memória

4. Periférico para periférico.

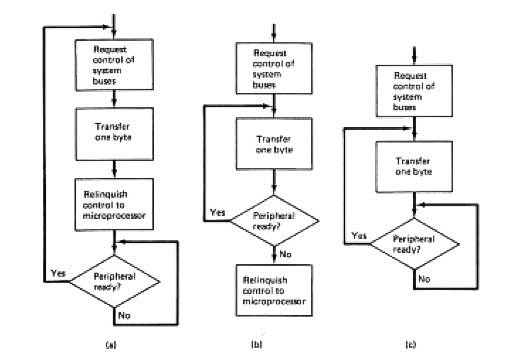

Normalmente é feita a interface do DMAC para o microprocessador como uma porta de I/O. Antes de ocorrer qualquer transferência de informação, o CPU deve programar o DMAC para o tipo de transferência que vai ocorrer, os endereços de origem e de destino e o número de bytes que vai ser transferido. Considerando que o DMA sequencial e simultâneo são “classes” separadas, existem três modos de DMA existentes em cada classe. A figura abaixo mostra estes três modos.

No modo simples ou de único byte - a) - o DMAC após ter o controlo dos barramentos do sistema, transfere um único byte de informação. O controlo dos barramentos é depois abandonado até a flag READY do periférico estar novamente activa.

O modo de pedido ou burst – b) – é usado quando os periféricos têm buffers de alta velocidade. Após ter ganho o controlo dos barramentos, é transferida a informação até que a flag READY do periférico deixe de estar activa. O controlo dos barramentos é então abandonado para o CPU. Quando READY estiver de novamente activa, ocorre outra explosão de DMA. A vantagem desta técnica é que o buffer pode ser preenchido rapidamente pelo DMAC e depois esvaziado ao prazer do periférico.

Um terceiro modo de DMA é

chamado modo contínuo ou de bloco – c). Este é

semelhante ao modo de pedido excepto que neste caso não é abandonado

o controlo dos barramentos até que seja transferido todo o bloco de

informação. Esta técnica é muito eficaz com um

periférico de alta velocidade que consiga acompanhar o DMAC.

Periféricos lentos fazem com que haja longos períodos de inactividade

dos barramentos enquanto o DMAC espera pela flag READY. Como o pedido de DMA

é amostrado no fim de cada ciclo de máquina (não ciclo

de instrução), o tempo de resposta do DMAC não será

maior que um ciclo de máquina mais um estado T.

O projecto de um controlador de DMA não é uma

tarefa fácil e é provavelmente a maior desvantagem desta técnica.

De facto o DMAC é um processador de transferência altamente especializado,

competindo com a própria complexidade do microprocessador.