O

que é ?

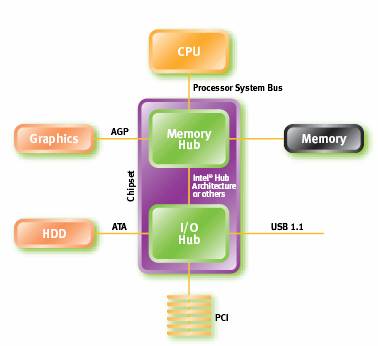

bus pci foi um bus de grande

importância nos últimos 10 anos e também o será nos próximos. No entanto, os

processadores e periféricos I/0 de hoje e de amanhã, exigem cada vez mais

largura de banda que não pode ser obtida à custa de futuras evoluções da

arquitectura pci actual. Os presentes esforços para criação de

bus pci foi um bus de grande

importância nos últimos 10 anos e também o será nos próximos. No entanto, os

processadores e periféricos I/0 de hoje e de amanhã, exigem cada vez mais

largura de banda que não pode ser obtida à custa de futuras evoluções da

arquitectura pci actual. Os presentes esforços para criação de tipos de bus com larguras de bandas elevadas, resultaram na arquitectura de

computadores que hoje em dia conhecemos, e que se encontra esquematizada na

figura ao lado.

tipos de bus com larguras de bandas elevadas, resultaram na arquitectura de

computadores que hoje em dia conhecemos, e que se encontra esquematizada na

figura ao lado.

À medida que o bus dos sistemas dos

processadores, continua a aumentar a frequência e a voltagem, também a largura

de banda das memórias tem vindo a aumentar para tentar acompanhar a evolução dos

processadores. Uma vez que o bus de memória costuma mudar em cada geração de

processadores, tradicionalmente encontram-se chips que procuram dividir os hubs

de memória e os hubs de I/0 .

Trata-se no entanto de um modelo

esgotado , dado que a tecnologia de sinalização do pci não pode nem aumentar a

frequência nem diminuir a voltagem. Isto deve-se ao facto de as transferências

síncronas de dados por cada ciclo de relógio se encontrarem condicionadas pelo

tipo de sinalização usada e pela rota que o sinal toma quando é transmitido.

Estudos que se vêem efectuando desde 1990 mostram que apenas se conseguiria um

pequeno aumento de performance à custa de soluções muito caras. Assim a

alternativa para evolução do bus pci passava pela definição de um novo tipo de

bus.

O PCI Express workgroup , constituído

por Intel™,Compaq™,Dell™, IBM™,Pci-Sgi™, encontra-se a trabalhar no

desenvolvimento de uma nova arquitectura I/0 de série.

Esta arquitectura será num futuro

próximo, a substituta da velhinha pci, à medida que as grandes companhias a

forem adoptando, o que deverá acontecer devido ao aumento das necessidades de

largura de banda, velocidade e escalabilidade.

A arquitectura PCI Express será uma

arquitectura generalista e de alta velocidade para ligação em série de

interfaces I/0 . Esta arquitectura terá capacidade para :

-

Evoluir até frequências na ordem dos 10Gbit por segundo;

-

Suportar múltiplas larguras de banda ou múltiplas

lanes(1,2,4,8,…32)

-

Evoluir até aos limites do cobre.

-

Oferecer a máxima largura de banda possível por pin, o

que não só diminui o custo como permite pequenos “form factors”.

-

Suporte para ligação chip a chip ou board a board.

-

Lidar com diferentes tipos de dados provenientes da

gestão de energia ,de sistemas de qualidade de serviço, da gestão de erros, ou

da integridade de dados.

-

Suportar módulos hot plug e hot swappable.

-

Ser um modo coerente de ligar dados, memórias e cabos em

soluções de clusters.

O modelo de software a seguir por esta

arquitectura será o já estabelecido pelo pci para o software e suportará ainda

módulos add-in, assim como plug-n-play.

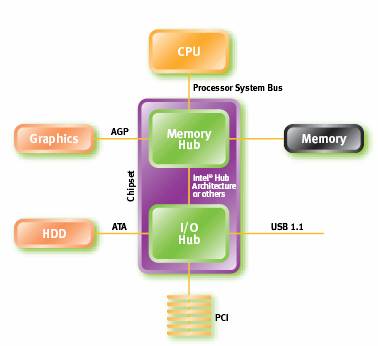

bus pci foi um bus de grande

importância nos últimos 10 anos e também o será nos próximos. No entanto, os

processadores e periféricos I/0 de hoje e de amanhã, exigem cada vez mais

largura de banda que não pode ser obtida à custa de futuras evoluções da

arquitectura pci actual. Os presentes esforços para criação de

bus pci foi um bus de grande

importância nos últimos 10 anos e também o será nos próximos. No entanto, os

processadores e periféricos I/0 de hoje e de amanhã, exigem cada vez mais

largura de banda que não pode ser obtida à custa de futuras evoluções da

arquitectura pci actual. Os presentes esforços para criação de tipos de bus com larguras de bandas elevadas, resultaram na arquitectura de

computadores que hoje em dia conhecemos, e que se encontra esquematizada na

figura ao lado.

tipos de bus com larguras de bandas elevadas, resultaram na arquitectura de

computadores que hoje em dia conhecemos, e que se encontra esquematizada na

figura ao lado.