Esta parte cobre todos os passos básicos para criar e simular um projecto de Verilog no VeriLogger Pro. Note–se que estes são os passos para um utilizador iniciado. Para informação mais detalhada consulte a ajuda do VeriLogger Pro. Para além disso, diversos diálogos possuem ajuda de contexto que permitem saber mais acerca das opções disponíveis. Para a usar basta clicar no botão com o ponto de interrogação, no canto superior direito, e depois no item a explicar.

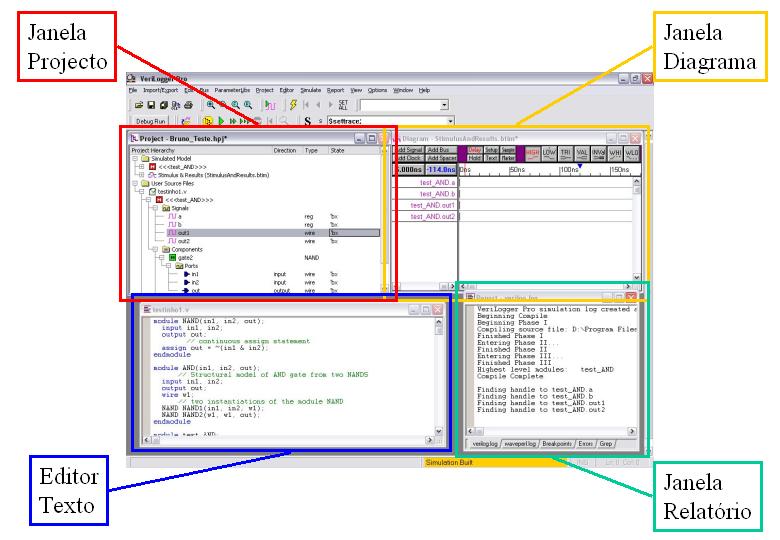

Em baixo, temos a organização comum de uma janela comum no VeriLogger Pro. Os nomes das janelas são indicativos e servem para referência interna neste documento.

Capítulo 1. Começar o Projecto

O simulador do VeriLogger Pro usa projectos para controlar a simulação e definir os ficheiros para serem simulados.

Para começar um projecto no VeriLogger Pro:

- Seleccione Project > New Project nos menus para abrir a janela de diálogo New Project Wizard. Escolha o nome do projecto e respectiva directoria e feche a janela. Isto irá criar uma árvore de projecto vazia.

Repare nos itens Project > Save Project e Project > Open Project no menu. Provavelmente irá utilizá-los bastantes vezes.

Capítulo 2. Adicionar Ficheiros de Modelos Verilog ao Projecto

Agora pode criar ficheiros de modelos Verilog e adicioná-los ao projecto.

Para criar um novo ficheiro Verilog:

- Seleccione o item Editor > New HDL File para abrir um editor de texto. Escreva o código e salve o ficheiro. Normalmente grava-se o ficheiro na directoria do projecto, mas tal não é obrigatório.

Adicionar o ficheiro ao projecto:

- Faça clique com o botão direito no editor e escolha Add to Project do menu de contexto. O nome do ficheiro ficará listado na pasta User Source Files da janela do projecto.

- Os ficheiros também podem ser adicionados usando o menu de contexto da janela de projecto. Clique com o botão direito na pasta User Source Files, e seleccione Add HDL File(s) para abrir uma nova janela, escolha os seus ficheiros e confirme.

O menu Editor contém funções para agir sobre os editores de texto. Um duplo clique sobre o nome de um ficheiro fonte na janela de projecto, abre automaticamente um editor de texto.

Capítulo 3. Compilar o Projecto

Quando os ficheiros são adicionados ao projecto, pode ver-se o seu nome, mas não a organização hierárquica dos módulos nele definidos. Para tal, primeiro deve-se compilar ou correr a simulação. O comando build compila os ficheiros de Verilog e constrói a respectiva árvore. Este comando NÃO corre a simulação. Para projectos grandes, build permite gerar a árvore sem esperar que a simulação corra.

Existem três maneiras de compilar o projecto:

- Clicar no botão amarelo ![]() na barra de simulação,

na barra de simulação,

- Seleccionar o item de menu Simulate > Build,

- OU, usar a tecla <F7>

Depois do projecto compilado podem ver-se todos os módulos, sinais, portas e componentes em cada ficheiro. Um modulo fica com o nome rodeado por parêntesis <<<nome>>>. Este é o módulo de nível mais alto. Todos os sub-módulos podem ser vistos ao descer na árvore deste módulo.

Depois de compilar o projecto, os sinais ou portas do módulo de nível mais alto são automaticamente adicionadas á janela de Diagrama. Se o módulo não tiver portas, são os sinais internos a ser apresentados. Se tiver, as portas de entrada aparecem como sinais a negro e as de saída como sinais púrpura. O sinais de entrada podem ser editados para fornecer estímulo ao módulo de nível de topo.

A capacidade de desenhar formas de onda e simular imediatamente é uma das características únicas do VeriLogger. Se o módulo de topo tiver portas, o projecto encaixa-o automaticamente num ficheiro de teste e cria sinais para testar os resultados. Isto torna rápido o processo de testar pequenas partes do modelo antes deste estar completo.

Capítulo 4. Teste ao Nível de Unidade (Desenhar stimulus)

Se o módulo de topo tiver portas de entrada, VeriLogger Pro pode desenhar formas de onda e gerar ficheiros de teste que podem ser usados para testar o modelo.

Os quarto passos básicos para o teste de nível de unidade são:

- Construir um projecto em VeriLogger Pro com um módulo de topo com portas de entrada. Isto irá preencher o diagrama StimulusAndResults com sinais negros de entrada e sinais púrpura de saída.

- Desenhar formas de onda nos sinais negros de input.

- De cada vez que uma simulação é corrida, VeriLogger Pro cria um módulo de teste a partir das formas de onda desenhadas e um módulo envolvente que liga tudo e simula.

VeriLogger tem dois modos de simulação, Auto Run e Debug Run que determinam quando a simulação é executado. O modo de simulação actual é exibido na barra de simulação. No modo Debug Run, as simulações começam apenas quando o utilizador clica nos botões Run ou Single Step (similar a uma simulação normal em Verilog). No modo Auto Run, o simulador corre a simulação automaticamente de cada vez que um sinal é adicionado ou alterado na janela de Diagrama. Neste modo é pratico testar pequenos módulos e fazer testes numa abordagem bottom-up. Para iterar entre modos basta clicar no botão de modo.

Capítulo 5. Monitorizar Sinais e Componentes

VeriLogger tem duas formas principais de exibir os resultados de uma simulação. A primeira é o ficheiro verilog.log na janela de Relatório que captura mensagens do simulador e quaisquer instruções no código que causem output. A segunda é o diagrama StimulusAndResults que apresenta os resultados da simulação de forma gráfica uma forma de onda.

Para ver o ficheiro de log:

- Clicar no tabulador verilog.log na janela de Relatório. Se a janela não aparecer, seleccionar a opção Window > Report para a fazer aparecer.

Os sinais observados são apresentados na janela de Diagrama StimulusAndResults. Para adicionar mais sinais, a observar, ao diagrama:

- Clicar no mais à esquerda do modulo de topo <<<nome>>>. Isto expande a árvore de nível de top.

- Expandir a árvore até encontrar sinais ou componentes a monitorizar.

- Clicar com o botão direito para abrir o menu de contexto.

- Seleccionar a opção Watch Connection or Watch Component. Isto adiciona o sinal à janela de Diagrama. Se um componente estiver for seleccionado, então todos os sinais de nível de topo desse componente serão adicionados à janela de Diagrama.

O diagrama StimulusAndResults guarda a lista de sinais observados e resultados da simulação.

Capítulo 6. Simular o projecto

Para similar o projecto:

- Clicar no botão Run ![]() na barra de simulação,

na barra de simulação,

- Seleccionar a opção no menu Simulate > Run,

- OU, usar a tecla F5.

Depois do projecto simulado, as formas de onda aparecem na janela de Diagrama. Para parar de observar um determinado sinal clique na janela de Diagrama no nome do sinal e pressione a tecla <Delete>.

Capítulo 7. Fazer Debug ao Projecto

No VeriLogger existem dois locais para verificar o estado da simulação. O indicador de estado de simulação na barra de botões e a barra de estado no canto inferior direito. Se no botão aparecer Simulation Error ou Compile Error, então existem erros nos ficheiros fonte do projecto.

Se a simulação falhar existem

dois locais diferentes na janela de Relatório que podem ser consultados para

descobrir a razão. O primeiro é o ficheiro verilog.log. Este ficheiro tem toda

a informação acerca da corrente simulação. O segundo é o tabulador Error. Este

tabulador mostra os erros de forma mais concisa.

Para localizar um determinado

erro:

- Clicar no tabulador Error da janela de Relatório para mostrar informação sobre os erros.

- Fazer duplo clique sobre um erro. Isto abre o ficheiro com erro na linha com o mesmo.

Capítulo 8. Usar breakpoints e debug passo-a-passo

No VeriLogger Pro é possível utilizar breakpoints, debug passo-a-passo, e instruções $display.

Para definir breakpoints no código:

- Abrir o ficheiro de Verilog no editor de texto.

- No editor e texto, existe uma barra cinzenta à esquerda do código, esta é a área dos breakpoints.

- Clicar nessa área, na linha de código onde a simulação deve parar. Isto faz com que apareça uma bolinha vermelha junto á área de breakpoints e com que o breakpoint seja listado no tabulador Breakpoints na janela de Relatório.

Nota: Os breakpoints são removíveis usando o mesmo processo.

Existem dois botões para execuções passo-a-passo:

![]() O botão Step over Calls indica que a próxima

linha de código a ser executada é a seguinte no nível actual.

O botão Step over Calls indica que a próxima

linha de código a ser executada é a seguinte no nível actual.

![]() O botão Step into Calls indica que o

próximo passo se prolonga até ao nível seguinte de código.

O botão Step into Calls indica que o

próximo passo se prolonga até ao nível seguinte de código.

O melhor é utilizar estas botões em conjunto com os breakpoints, assim, no caso de ciclos é possível simular até ao próximo breakpoint.

Existem ainda estes três botões para ajudar ao debug:

![]() O botão

Stop suspende a simulação.

O botão

Stop suspende a simulação.

![]() O botão

Restart interrompe a simulação actual e

limpa a janela de Diagrama. A simulação corre a partir da primeira instrução,

assim que qualquer dos botões para executar for pressionado.

O botão

Restart interrompe a simulação actual e

limpa a janela de Diagrama. A simulação corre a partir da primeira instrução,

assim que qualquer dos botões para executar for pressionado.

![]() O botão Goto abre um editor de texto,

na linha de código a ser executada.

O botão Goto abre um editor de texto,

na linha de código a ser executada.

VeriLogger Pro também suporta a instrução $display de Verilog. Assim, qualquer saídas destas instruções é exibida no ficheiro verilog.log na janela de Relatório

Capítulo 9. Salvar o Projecto, o Código e os Ficheiros Waveform

No VeriLogger existem três tipos de ficheiro associado com projecto de Verilog.

- Ficheiros de projecto têm extensão HPJ e salvam-se utilizando a opção Project > Save HDL Project. Isto salva a lista de ficheiros e as opções de simulação mas, NÃO salva as opções quanto aos ficheiros monitorizados.

- Ficheiros de código fonte de HDL normalmente têm extensões V e salvam-se seleccionando o editor de texto correspondente e utilizando a opção Editor > Save HDL Code.

- Diagramas StimulusAndResults têm extensão BTIM e salvam-se usando File > Save Timing Diagram. Neste ficheiro ficam guardados todos os sinais a ser monitorizados. Esta opção ajuda a criar diferentes casos de teste e fazer comparações e contrastes com simulações futuras